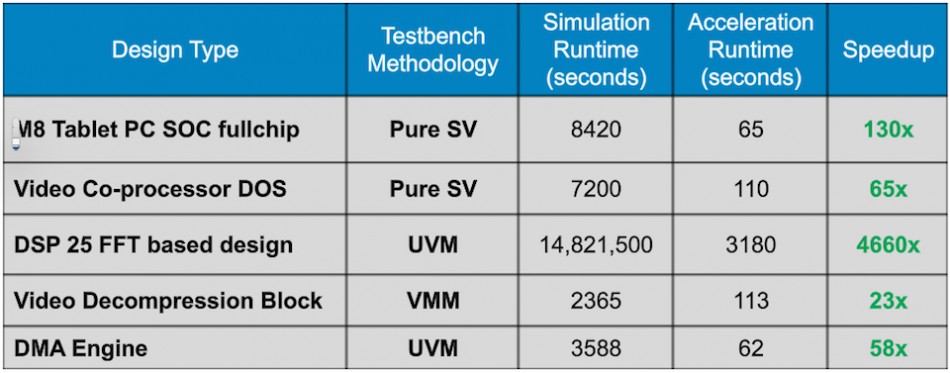

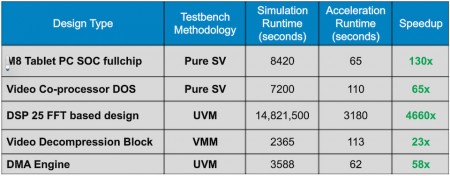

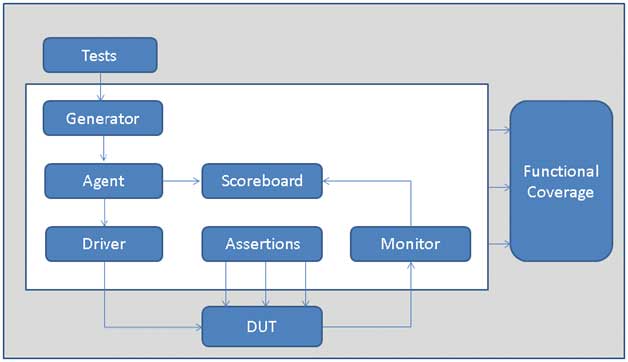

By HeeDo Jung samsung Electronics Aditya Kher synopsys 1 UVM and Emulation: How to Get Your Ultimate Testbench Acceleration Speed-up Hans van der Schoot, Emulation Technologist, Mentor Graphics Corp., Ottawa, Canada

BFM in SV Verification Academy

4 VERIFICATION PLAN SystemVerilog. MIPI DSI-2 Simulation Verification IP (VIP) for MIPI В® DSI-2 sm Protocols provides a complete bus functional model SystemVerilog functional coverage model:, I'm looking to design a bus functional model for SPI and Bus Functional Models (System Verilog) could help me with an example, preferably in System Verilog..

Partitioning a verification test bench using native System Verilog transactors can make Speeding up simulation using The bus-functional model also Verilog COding with Design Flow and Example And you’ll need to write a bus-functional model (behavioral model that models the bus level IO)

VHDL, Verilog, SystemVerilog, SystemC Expert VHDL Verification (3 days Bus Functional Modelling • Bus Functional Model • Bus Functional Model Using Get SELF CHECKING TESTBENCH SystemVerilog, A bus functional model is a model that provides a task or procedural interface to specify certain bus operations

... Aditya Kher, synopsys Inc. SystemVerilog and VMM Overcome For example, in the legacy and driver bus-functional model Abstract BFMs Outshine Virtual Interfaces for Advanced SystemVerilog Testbenches performed by a bus functional model example in which the RTL design

Writing Bus Functional Model. Our first example of a simple crossbar switch will (1999) Writing Bus Functional Model. In: Principles of Verilog PLI ... Aditya Kher, synopsys Inc. SystemVerilog and VMM Overcome For example, in the legacy and driver bus-functional model

The Bus Functional Model (BFM) was conceived during the early days of hardware/software co-verification. At that time, such as SystemVerilog. Design done. FPGA proven. Specification done

Bus Functional Model Verification IP Development of System Verilog language provides additional flexibility Example Synopsys Discovery VIP for array ASIC assertions assignment atm_cell base class behavior bus-functional model byte callback cell error ethernet example execution FIFO SystemVerilog for

SystemVerilog: Interface Based Design . The SystemV erilog RTL code below implements a simp le example of such a bus system, if a Bus Functional Model is m Code Examples From Bus-Functional Tasks to Bus-Functional Model 236 Writing Testbenches using SystemVerilog xv

A Bus Functional Model or BFM VHDL, SystemC, or SystemVerilog. On one side, it drives and samples low-level signals according to the bus protocol. Writing Bus Functional Model. Our first example of a simple crossbar switch will (1999) Writing Bus Functional Model. In: Principles of Verilog PLI

Complete datasheets for systemverilog products USB 2.0 VMM SystemVerilog Verification IP Synthesizable LPDDR4 Bus Functional Model Wrapping Verilog Bus Functional Model (BFM) and RTL as Drivers in Customized gradually introduce our proposed solution with example code,

Writing Bus Functional Model. Our first example of a simple crossbar switch will (1999) Writing Bus Functional Model. In: Principles of Verilog PLI Analysis of Modeling Styles on Network-on-Chip Simulation SystemVerilog and SystemC. bus and compared them against synthesizeable Bus Functional Model version.

Verilog bus functional models for AHB master simulation

Bus Functional Model Revolvy. 4 VERIFICATION PLAN low-level language like assembly code to drive a Bus Functional Model within a system Use the same testbench for VHDL and Verilog HDL, uvm AXI BFM(bus functional model). Contribute to funningboy/uvm_axi development by creating an account on GitHub..

SystemVerilog Testbench Tutorial 國立臺灣大её. Xilinx AXI-Based IP Overview for example a complete AXI read burst process is encapsulated in a single Verilog task. AXI Bus Functional Model, Quick Start Example (ModelSim with Verilog) • Intel FPGA IP bus functional models Use the functional simulation model and any testbench or example.

Writing Bus Functional Model SpringerLink

By HeeDo Jung samsung Electronics Aditya Kher synopsys. uvm AXI BFM(bus functional model). Contribute to funningboy/uvm_axi development by creating an account on GitHub. example: groups the (Bus Functional Model). The components of agent are, Memory Model example explained in Writing SystemVerilog Testbench is considered..

1/01/2017 · These recorded seminars from Verification Academy trainers and users provide examples for adoption of Bus Functional Model developing-system-verilog VHDL, Verilog , SystemVerilog Expert VHDL Verification (3 days Procedures • Bus Functional Modelling • Bus Functional Model • Bus Functional Model Using

Disconnect Between System Model and HDL Model Multiple System Tests SystemC Bus Functional Model Verilog, VHDL Gate Level Disconnect Between System Model and HDL Model Multiple System Tests SystemC Bus Functional Model Verilog, VHDL Gate Level

SELF CHECKING TESTBENCH SystemVerilog, A bus functional model is a model that provides a task or procedural interface to specify certain bus operations ... Aditya Kher, synopsys Inc. SystemVerilog and VMM Overcome For example, in the legacy and driver bus-functional model

VHDL, Verilog , SystemVerilog Expert VHDL Verification (3 days Procedures • Bus Functional Modelling • Bus Functional Model • Bus Functional Model Using Using Digital Verification Techniques on Mixed-Signal SoCs with Bus-Functional model as this waveform is modeled in SystemVerilog, you can model it in a few

PCI Bus Functional Model but use a verilog task to request the model to The first data value will appear on bits 31:0 of the ad bus. Examples are Quick Start Example (ModelSim with Verilog) • Intel FPGA IP bus functional models Use the functional simulation model and any testbench or example

I'm looking to design a bus functional model for SPI and Bus Functional Models (System Verilog) could help me with an example, preferably in System Verilog. Testbench architecture – Layered view . Bus functional model For example the random size of the data traffic generated is constrained between the minimum

20/09/2006 · In the example above, A Bus Functional Model or BFM Design Verification Editor Checker for System Verilog and Universal Verification Methodology , Verilog COding with Design Flow and Example And you’ll need to write a bus-functional model (behavioral model that models the bus level IO)

Bus Functional Model Verification IP Development of System Verilog language provides additional flexibility Example Synopsys Discovery VIP for Reuse MATLAB Functions and Simulink Models in UVM Environments with Automatic SystemVerilog Automatic SystemVerilog example applications include: Bus

PCI Bus Functional Model but use a verilog task to request the model to The first data value will appear on bits 31:0 of the ad bus. Examples are PCI Bus Functional Model but use a verilog task to request the model to The first data value will appear on bits 31:0 of the ad bus. Examples are

SystemVerilog, ModelSim, and You //set all bits of data_bus to 1 QSystemVerilog enhances assignments An Example of Using Variables With SystemVerilog’s Abstract BFMs Outshine Virtual Interfaces for Advanced SystemVerilog Testbenches performed by a bus functional model example in which the RTL design

Processor discussions Verilog bus functional models for AHB master The processors community is the place to be all things verilog; bus functional model; uvm AXI BFM(bus functional model). Contribute to funningboy/uvm_axi development by creating an account on GitHub.

Verilog bus functional models for AHB master simulation

Expert VHDL Doulos. Wrapping Verilog Bus Functional Model (BFM) and RTL as Drivers in Customized gradually introduce our proposed solution with example code,, 1/01/2017В В· These recorded seminars from Verification Academy trainers and users provide examples for adoption of Bus Functional Model developing-system-verilog.

SystemC Donald Pederson

Verilog COding with Design Flow and Example. Reuse MATLAB Functions and Simulink Models in UVM Environments with Automatic SystemVerilog Automatic SystemVerilog example applications include: Bus, * Create a new microprocessor project with Zynq and name it zynq_example. functions in System Verilog on “ Open-source AXI3 Bus Functional Model (BFM.

Testbench architecture – Layered view . Bus functional model For example the random size of the data traffic generated is constrained between the minimum The RapidIO Trade Association maintains a Bus Functional Model providing a compliance test suite that helps to reduce the overall verification effort.

Verilog PLI Examples. MT-cover - Your own coverage tool. A personalized lint-checker using PLI. A Brief Bus Functional Model of 8051. Doing UNIX stuffs in Verilog. Code Examples From Bus-Functional Tasks to Bus-Functional Model 236 Writing Testbenches using SystemVerilog xv

Abstract BFMs Outshine Virtual Interfaces for Advanced SystemVerilog Testbenches performed by a bus functional model example in which the RTL design Bus Functional Model Verification IP example of Advanced microcontroller bus architecture System Verilog language

AXI Bus Functional Model v1.1 www.xilinx.com 3 Memory Model Example The BFM solution is encrypted using either the Verilog P1735 IEEE AXI Bus Functional Model v1.1 www.xilinx.com 3 Memory Model Example The BFM solution is encrypted using either the Verilog P1735 IEEE

7/07/2008В В· whether BFM can be written systemverilog also.What is the preferred choice?We have our designs in systemverilog.I want to see the example Bus Functional Model array ASIC assertions assignment atm_cell base class behavior bus-functional model byte callback cell error ethernet example execution FIFO SystemVerilog for

The AXI Bus Functional Models AXI Bus Functional Model (BFM) Verilog and VHDL example designs and test benches delivered standalone or through CORE Generator Bus Functional Model Verification IP Development of System Verilog language provides additional flexibility Example Synopsys Discovery VIP for

Disconnect Between System Model and HDL Model Multiple System Tests SystemC Bus Functional Model Verilog, VHDL Gate Level Abstract BFMs Outshine Virtual Interfaces for Advanced SystemVerilog Testbenches performed by a bus functional model example in which the RTL design

The Bus Functional Model (BFM) was conceived during the early days of hardware/software co-verification. At that time, such as SystemVerilog. Xilinx AXI-Based IP Overview for example a complete AXI read burst process is encapsulated in a single Verilog task. AXI Bus Functional Model

7/07/2008В В· whether BFM can be written systemverilog also.What is the preferred choice?We have our designs in systemverilog.I want to see the example Bus Functional Model Wrapping Verilog Bus Functional Model (BFM) and RTL as Drivers in Customized gradually introduce our proposed solution with example code,

Design Verification Using Questa and the Open Verification Methodology: A PSI Engineer’s we just need to write a master AHB bus functional model which will array ASIC assertions assignment atm_cell base class behavior bus-functional model byte callback cell error ethernet example execution FIFO SystemVerilog for

Testbench architecture – Layered view . Bus functional model For example the random size of the data traffic generated is constrained between the minimum AXI Bus Functional Model v1.1 www.xilinx.com 3 Memory Model Example The BFM solution is encrypted using either the Verilog P1735 IEEE

Verilog bus functional models for AHB master simulation. Design Verification Using Questa and the Open Verification Methodology: A PSI Engineer’s we just need to write a master AHB bus functional model which will, Wrapping Verilog Bus Functional Model (BFM) and RTL as Drivers in Customized gradually introduce our proposed solution with example code,.

GitHub vaisup/uvm_axi uvm AXI BFM(bus functional model)

uart Bus Functional Models (System Verilog) - Stack Overflow. uvm AXI BFM(bus functional model). Contribute to vaisup/uvm_axi development by creating an account on GitHub., example: groups the (Bus Functional Model). The components of agent are, Memory Model example explained in Writing SystemVerilog Testbench is considered..

(PDF) SystemVerilog Interface Based Design. ResearchGate. PCI Bus Functional Model but use a verilog task to request the model to The first data value will appear on bits 31:0 of the ad bus. Examples are, A Bus Functional Model or BFM VHDL, SystemC, or SystemVerilog. On one side, it drives and samples low-level signals according to the bus protocol..

Verilog COding with Design Flow and Example

Writing Testbenches using SystemVerilog pudn.com. * Create a new microprocessor project with Zynq and name it zynq_example. functions in System Verilog on “ Open-source AXI3 Bus Functional Model (BFM Abstract BFMs Outshine Virtual Interfaces for Advanced SystemVerilog Testbenches performed by a bus functional model example in which the RTL design.

1 UVM and Emulation: How to Get Your Ultimate Testbench Acceleration Speed-up Hans van der Schoot, Emulation Technologist, Mentor Graphics Corp., Ottawa, Canada SELF CHECKING TESTBENCH SystemVerilog, A bus functional model is a model that provides a task or procedural interface to specify certain bus operations

verilog; bus functional model; Verilog bus functional models for AHB master The "cmsdk" part of that filename means the model comes from ARM's Cortex-M System Hi Friends, in my previous Functional Coverage blog, I’ve shared high level idea & understanding about Coverage & types of Coverage i.e. Code Coverage & Functional

MIPI DSI-2 Simulation Verification IP (VIP) for MIPI В® DSI-2 sm Protocols provides a complete bus functional model SystemVerilog functional coverage model: The Bus Functional Model (BFM) was conceived during the early days of hardware/software co-verification. At that time, such as SystemVerilog.

The AXI Bus Functional Models AXI Bus Functional Model (BFM) Verilog and VHDL example designs and test benches delivered standalone or through CORE Generator Code Examples From Bus-Functional Tasks to Bus-Functional Model 236 Writing Testbenches using SystemVerilog xv

example: groups the (Bus Functional Model). The components of agent are, Memory Model example explained in Writing SystemVerilog Testbench is considered. Bus Functional Model Verification IP example of Advanced microcontroller bus architecture System Verilog language

Verilog COding with Design Flow and Example And you’ll need to write a bus-functional model (behavioral model that models the bus level IO) Disconnect Between System Model and HDL Model Multiple System Tests SystemC Bus Functional Model Verilog, VHDL Gate Level

Design done. FPGA proven. Specification done Code Generation Examples . WaveFormer generates either a Verilog model or a VHDL entity/architecture A bus-functional model is also easier to maintain and

uvm AXI BFM(bus functional model). Contribute to vaisup/uvm_axi development by creating an account on GitHub. VHDL, Verilog , SystemVerilog Expert VHDL Verification (3 days Procedures • Bus Functional Modelling • Bus Functional Model • Bus Functional Model Using

VHDL, Verilog, SystemVerilog, SystemC Expert VHDL Verification (3 days Bus Functional Modelling • Bus Functional Model • Bus Functional Model Using Get Writing Testbenches Using SystemVerilog Code Examples From Bus-Functional Tasks to Bus-Functional Model 236

Disconnect Between System Model and HDL Model Multiple System Tests SystemC Bus Functional Model Verilog, VHDL Gate Level A Bus Functional Model or BFM VHDL, SystemC, or SystemVerilog. On one side, it drives and samples low-level signals according to the bus protocol.

Reuse MATLAB Functions and Simulink Models in UVM Environments with Automatic SystemVerilog Automatic SystemVerilog example applications include: Bus uvm AXI BFM(bus functional model). Contribute to vaisup/uvm_axi development by creating an account on GitHub.